RESEARCH & DEVELOPMENT (R&D)

Silicon Interfaces® teams have undertaken Research and Development in diverse areas. like Power Verification™ - UPVM© - Low Power Class-based Library, Scaling down Fault Simulation cycle time using Artificial Intelligence and Machine Learning modeling techniques, PCIe Race Condition resolution with Data Integrity/Security using Memory Manager and Fabric Matrix. These research areas have been undertaken by Silicon Interfaces Research Engineers to solve specific problems in domains of early stage Low Power Verification, application AI/ML to Fault Simulation, Data Integrity/Security as well multi-Core ALU enhcancements using Vedic Multipliers. The Research findings have been presented in several Conferences in North America, Europe, and Asia Pacific:

Power Verification™ - UPVM© - Low Power Class-based Library

- Introduction

- Industry seems to be following a parallel path with respect to:

- Methodologies (UVM) based test bench

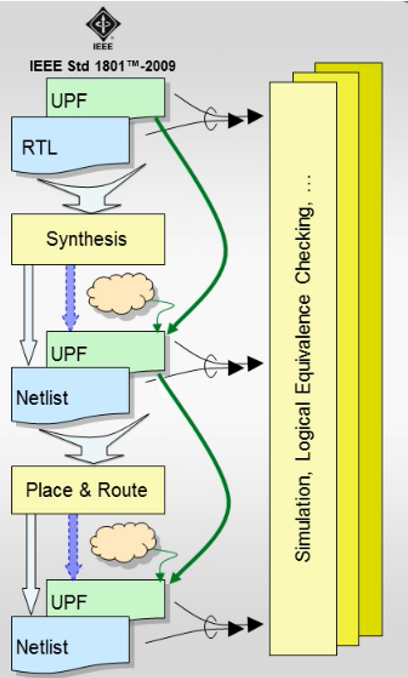

- Power Architecture, including Unified Power Formats (UPF)

- Both are fundamental requirements to IP, ASIC, Chiplet and SOC verification especially in the power saving mobile world.

- Incorporating Power Architecture seems to be more like an afterthought post Functional Verification, almost a fourth dimension to our strategy leveraging the test bench architecture.

- Leading EDA tools providers tend to have tools with Functional Simulation with UVM switches and a separate Low Power and Power Aware strategies.

- It would be more efficient to do Methodologies based Functional Verification and Coverage along with Low Power Implementation.

- Main Idea

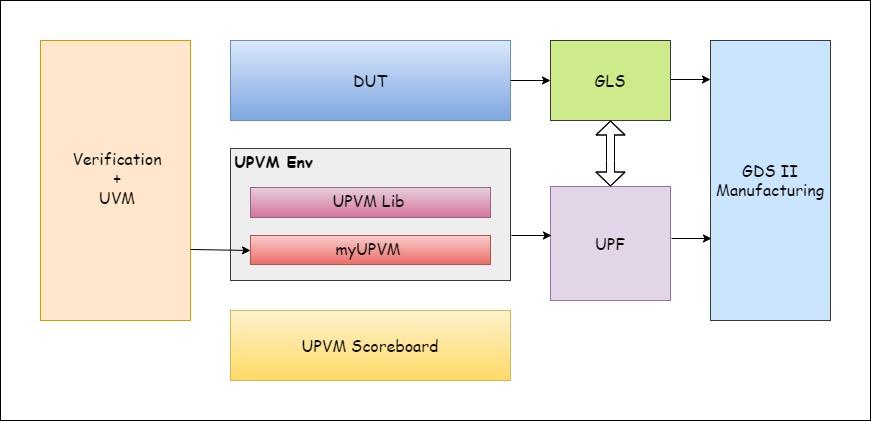

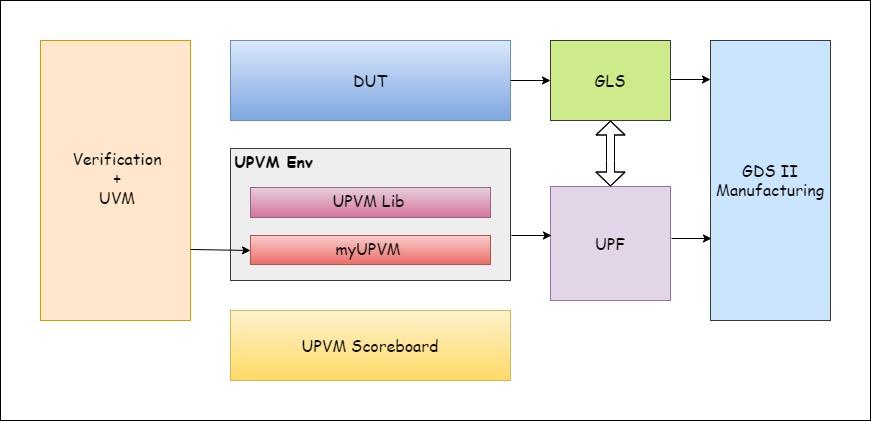

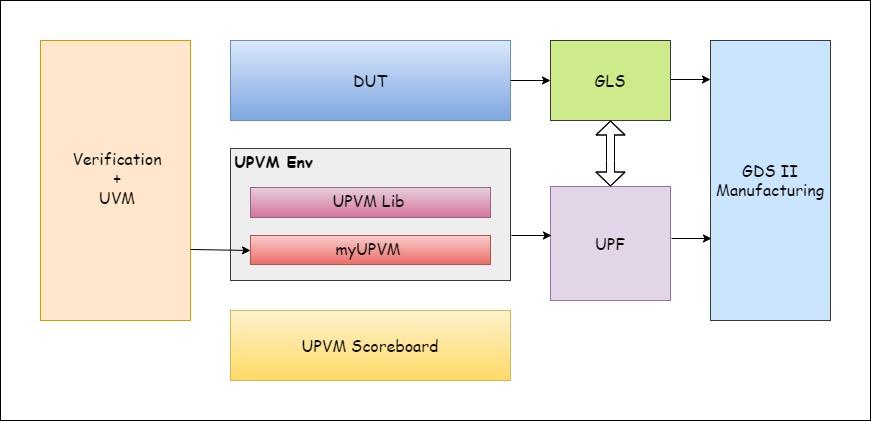

- UPVM is an emerging standard library for unified Power Verification™ within the SV/UVM environment for the purposes of early-stage integration of power management and strategies (along with DUT Design/Verification) and has

- a standard library package consisting of SV Classes for power management/strategies

- a myUPVM templates wherein the Low Power Designer extends the Library Package Classes for the DUT under consideration

- a structured query based automation tool which generates an intermediate file for the myUPVM templates to be populated configuring the power strategies for the DUT

- UPVM Class for standard Low Power validation Class which may be extended in UPVM Scoreboard for validating power strategies and mapping.

- generate a UPF file on compilation and simulation of the full SV Code.

- Intent of UPVM is Low Power Verification – responsibilities end once we have verified the Design.

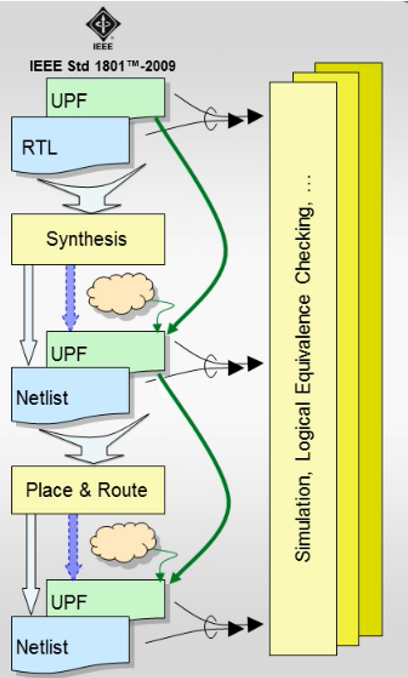

- UPVM to RTL, GLS, GDSII - Handover to Tier1 Industry leading tools for Low Power Standard Low Power/Aware tools further the implementation flow from RTL, GLS and GDSII

- The effort is to interleave Functional Verification Methodology and Power Architecture in SystemVerilog, like a single existing and widely deployed methodologies-based platform, like UVM.

- Recognizing that customizing template for DUT under consideration may be a tedious task, a Python based tool has been development to ease the process.

- aUPVM – Implementation

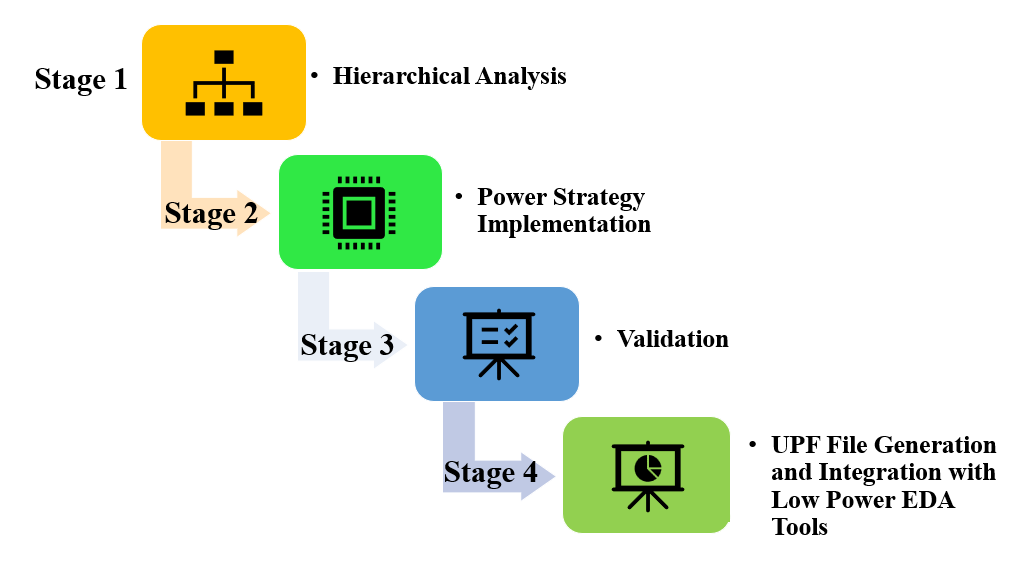

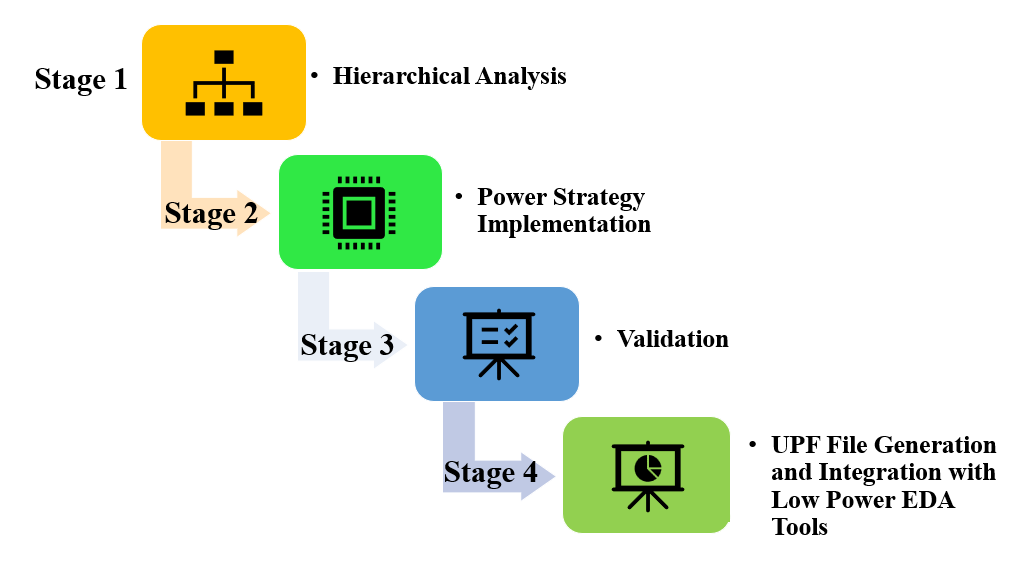

- Step-by-Step Automation for Power Verification with Functional Correctness:

- Stage 1: Hierarchy Analysis with Python Script

- Initiate the process of employing Python-based tool to analyze the design hierarchy with and set_directory.

- Extracted Hierarchy guides the selection of set_design_top and set_scope, influencing power domain decisions.

- The Code Management constructs for load_upf and save_upf is incorporated.

- Stage 2: Implementation of Power-Saving Strategies within the Python Script

- Implementing power domains, ports, supply sets, and power-saving strategies like retention, isolation, and level shifters.

- Automation scripts remain pivotal, ensuring optimal power configuration throughout the design.

- Stage 3: Reading the Python intermediate file outputs in SystemVerilog

- In this stage the SystemVerilog myUPVM modules interfaces with UPVM SV library, reads the python generated internal format output file and collects the data to customize myUPVM template modules.

- Scoreboard will compare the library data and analyse to see if any power contradictions are present.

- Stage 4: Automation Resumes for UPF File Generation

- Generate a custom UPF file based on the extracted data.

- Stage 5: Integration with Low Power EDA Tools

- Culminate the Process in Stage 5 by integrating the SV generated UPF file with Low Power EDA tools where then continues the journey for UPF post synthesis and backend layouts.

- Advantages of UPVM™

- OOPS-based

- Low Power, now within SV/UVM environment which Power Verification Engineers already know

- Power Verification is UPF-based.

- No need to learn UPF Constructs.

- Verification/Validation at early stage whilst verifying the UVM.

- Lower learning curves to learn Low Power tools, since the Library has python scripts to automate myUPVM

- UPF generation and integrate with tools for verification at RTL, GLS and GDSII as per IEEE standards.

- The subject matter described here in subject to copyrights and patentable ideas and it is recommend that you click here to contact Silicon Interfaces for more information and an NDA for “Power Verification™ - UPVM© - Low Power Class-based Library”